联系我们

与泰克代表实时聊天。 工作时间:上午 9:00 - 下午 5:00(太平洋标准时间)。

电话

致电我们

工作时间:上午9:00-下午5:00(太平洋标准时间)

下载

下载手册、产品技术资料、软件等:

反馈

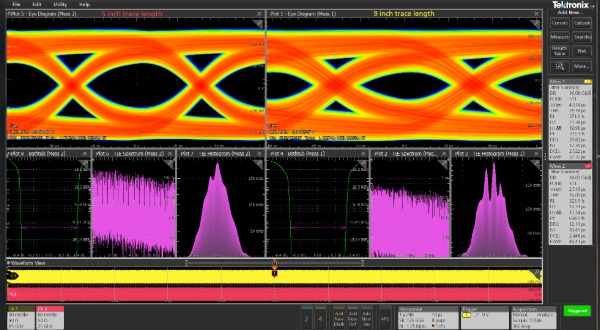

自动化测试和调试

高速数字标准正在迅速发展,以支持数据驱动世界的性能需求。下一代串行标准和数据通信要求带来了新的测试挑战,突破了当今合规性和调试工具的极限。从设计和模拟、分析、调试到一致性测试,泰克提供自动化电气测试解决方案,以优化性能、加快验证周期并加速产品上市。

对高性能计算标准进行准确、可重复的测试

在数据中心、人工智能 (AI) 和高性能计算等数据密集型市场中,对更高数据吞吐量和更大存储容量的需求持续增长。更高的数据传输速率带来了复杂的设计,这些设计突破了信号完整性的界限,并需要进行更高的性能测量才能实现一致性以及进行调试和验证。泰克的自动化测试解决方案确保准确性和可重复性,使工程师能够应对这些挑战,从而测试他们的最新设计。

缩短了测试消费类技术的时间

创新的步伐正在刺激对更新、更快的消费类设备的需求。开发这些设备所依据的标准在提高数据速率和设计复杂性方面带来了新的测试挑战。泰克测试解决方案提供准确、可重复的测量,并缩短了测试时间,确保符合最新的规格。

用于以太网设备设计的全面工具

以太网为包括超大规模数据中心和企业系统以及汽车和工业应用在内的各种应用场合提供网络连接。泰克提供全套工具,支持在这些生态系统中测试、开发和调试 IEEE 802.3 以太网设备的物理层。

Resources

Webinar

Webinar