联系我们

与泰克代表实时聊天。 工作时间:上午 9:00 - 下午 5:00(太平洋标准时间)。

致电我们

工作时间:上午9:00-下午5:00(太平洋标准时间)

下载

下载手册、产品技术资料、软件等:

反馈

分析电源分配网络 (PDN) 上的电源完整性

配电网 (PDN) 必须为微处理器、DSP、FPGA 和 ASIC 等灵敏负载提供多条低噪声直流电源轨。追求更高速度和更高密度意味着更快的边沿速率、更高的频率和更多的电源轨,以及更低的电压电平和更高的电流。这给信号完整性和电源完整性的设计带来了压力。

电源完整性测量旨在验证达到负载点 (POL) 的电压和电流在所有预期工作条件下是否满足负载的电源轨规格。需要特别注意的是,在 GHz 频率下准确测量电源轨噪声(毫伏)。

在不阻断直流电或给电源轨带来过大负载的情况下测量高频纹波

噪声测量是电源完整性分析的重要环节。电源轨的噪声参数可以达到MHz或GHz频率范围,而电压幅值是毫伏级,这给测量带来了挑战。

低噪声高带宽的示波器可以进行这些测量,但将信号输入到仪器中并非易事。

示波器随附的高阻抗10X无源探头可能具有足够的带宽,但它们会衰减您试图测量的噪声信号。

1X探头可以无衰减地传递噪声信号,但其带宽范围仅限于几MHz。输入阻抗为50 Ω的传输线探头或电缆具有很好的高频性能,但在直流时会产生很大负载。

用于电源轨测量的理想探头应在直流时具有高阻抗,而在高频时充当50 Ω传输线。TPR1000和TPR4000等电源轨探头就专为应对这些挑战而设计,具有高带宽、低衰减和最小负载效应。

处理 1 V 至 48 V 及以上的电源

尽管许多 FPGA 和 SoC 的主电源电压已经大幅下降,但这些不是唯一要考虑的 电源。片上 I/O 电源的覆盖范围比主逻辑电源的覆盖范围大得多。为 POL 稳压器或电压调节器模块 (VRM) 供电的整体 电源的电压通常要高得多。

尽管许多示波器和探头可以提供一定的 DC 偏移,但可能不足以处理系统中的所有电源 轨。在较低的伏特/格(较高灵敏度)设置下,仪器系统往往能 减少偏移。虽然可选择阻断直流电,但这通常是不可取的(请参见上文)。

除了满足上面概述的高频需求外,TPR1000 和 TPR4000 等电源轨探头还可提供高偏移范围以应对各种电压电平。

测量电源分配网络阻抗

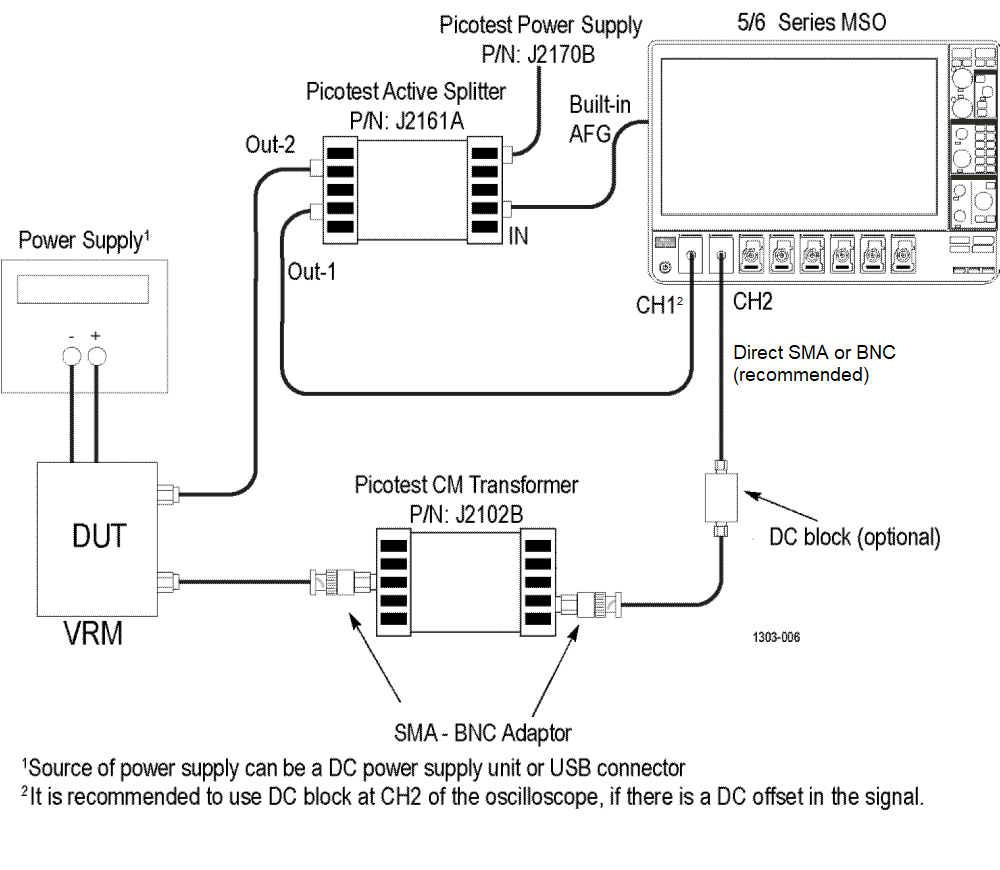

测量 10 mV 量级的噪声需要特别注意测量系统噪声。如上所述, 使用非衰减探头或 1X 探头可以减轻示波器放大器的负担。示波器的 内部噪声和测量分辨率也起着至关重要的作用。

6 系列 MSO 包括具有行业领先噪声性能的新前端。示波器的开放 信道噪声低至 50μVRMS和 466μV 峰值。当与 TPR1000/4000 电源 轨探头配对时,系统噪声可低至 70μVRMS。

6 系列以 12.5 GS/s 的速度提供 12 位分辨率。高分辨率功能可在 625 MS/s 及以下速度将分辨率提高到 16 位。4 和 5 系列 MSO 还提供 12 位分辨率,在使用高分辨率模式的条件下最高可达 16 位。

测量电源分配网络阻抗

为 FPGA、处理器和其他复杂集成电路供电的电源分配网络,电源轨阻抗必须很低,才能提供大电流以响应快速变化的需求。但是,网络内许多部件都会产生阻抗,包括稳压器、解耦电容和PCB走线。所以阻抗测量也是电源完整性分析的重要环节。高速开关涉及宽带频率,并且阻抗的意外变化会导致瞬变或噪声过大。在较宽的频率范围内测量网络设计的阻抗可确保网络不会发生意外情况。

传统上,网络阻抗测量使用双端口 TTR500 等 VNA 进行, 测量范围从 100 kHz 到 6 GHz。

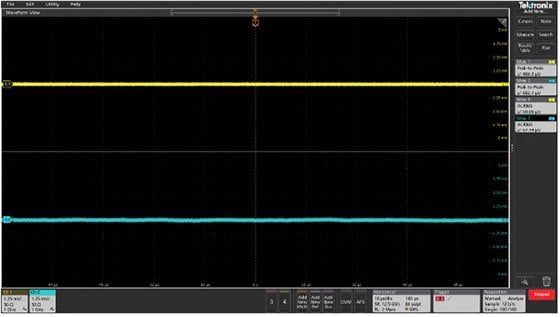

5和6系列MSO示波器可以使用分析软件、 信号发生器(内置或使用AFG31000系列产品)和隔离变压器来在较宽的频率范围内测量电源轨阻抗。频率可低至10 Hz,高至50MHz(内部信号发生器),或AFG31000系列的最大值。

电源轨噪声影响时钟和数据信号抖动

假设您已经测量了电源轨噪声,并且测量值超出了规格。那么,这是由什么引起的呢? DC-DC 转换器?整体供电?PLL?时钟?还是串扰?频谱分析可以提供噪声 源的线索 – 有助于将噪声频率与开关频率和谐波相关联。

频谱分析仪(例如 RSA306)通过直流模块连接到电源轨,可帮助您深入了解

噪声。

示波器上的 FFT 功能也很有用,但这些功能使用示波器上的采样时钟,致使

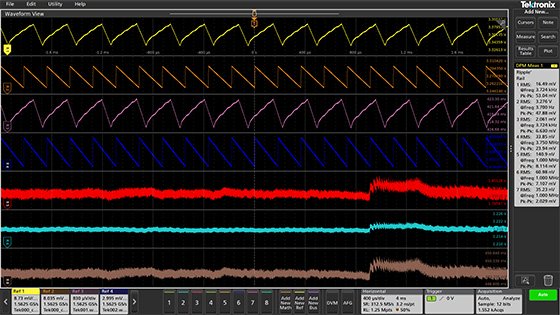

难以或无法同时查看频谱和电压波形。4、5 和 6 系列 MSO 上的

独特频谱视图提供了独立的频谱分析仪控件,因此您可以同时查看同步的时域

频谱和频域波形。

电源轨噪声影响时钟和数据信号抖动

电源轨上的噪声通常会转化为高速数据线上的抖动。应在时域和频域都对抖动和电源完整性进行分析。将时间间隔误差 (TIE) 频谱中的周期性抖动频率与功率纹波频谱中的尖峰进行比较,可快速准确识别由电源分配网络 (PDN) 引起的信号完整性问题。这类分析需要示波器具备良好的频谱分析能力和抖动分析能力。

/fig-07-powerrailripple.png?h=548&iar=0&w=975)

借助自动化分析软件更快地进行电源轨测量

在几十条电源轨上,即使是进行简单的测量(例如,纹波、过冲和下冲)也需要 大量时间和注重细节。

5 和 6 系列 MSO 随数字电源管理软件一起提供,可自动执行这些重复的 测量并生成深度报告。该软件还包括抖动分析(TIE、RJ、DJ 和 Eye 测量),以便检查由 PDN 供电的时钟和通信信号是否存在过多抖动。

电源完整性分析参考系统

6系列B MSO示波器

噪声超低、具有12位分辨率和多达8个通道。频率范围1-10 GHz。内置任意函数发生器 (AFG),适用于阻抗测量。

噪声分析

-

数字电源管理和分析 (DPM) 软件

可自动进行纹波、过冲、欠冲、开通、关断、时间趋势、建立时间和抖动测量 -

电源轨探头

-60 to +60 Vdc低噪声,频率高达4 GHz,直流偏置范围广:-60V-+60V。

阻抗分析

-

功率测量和分析 (PWR) 软件

针对电能质量、谐波、振幅、时序、开关损耗、磁性和频率响应(控制回路、PSRR和阻抗),进行测量和分析 -

有源功率分离器(如Picotest J2161A)

将信号从示波器内的任意函数发生器分离到示波器输入通道和被测电源轨 -

共模变压器(如Picotest J2102B-BNC)

两端口分流测阻抗时消除接地回路误差